## Reduced Graphene Oxide Electrodes for Large Area Organic Electronics

Paul H. Wöbkenberg, Goki Eda, Dong-Seok Leem, John C. de Mello, Donal D. C. Bradley, Manish Chhowalla, and Thomas D. Anthopoulos\*

Devices based on solution processable organic materials are promising for inexpensive large area electronics on transparent flexible plastic substrates.<sup>[1]</sup> In practice, however, electrodes in organic devices typically consist of vacuum deposited materials that are largely incompatible with this goal. The most widely used transparent electrode for plastic electronics to date is tin-doped indium oxide (ITO). The latter provides a relatively high electrical conductivity ( $\approx 10^4$  S cm<sup>-1</sup>)<sup>[6]</sup> with good optical transparency (>80%) for visible light.[7] Furthermore ITO has been used widely on plastic substrates, being compatible with high-throughput deposition processes such as sputtering. However, there are problems associated with ITO: i) it is brittle, which leads to micro-cracking when it is flexed and a consequent drop in conductivity, ii) there are concerns over the increasing cost of indium (rising from ≈350 to ≈1000 US\$ per kg in recent years)<sup>[8]</sup> and its limited abundance, and iii) it is primarily suited to use as an anode material only because of its high work function. Hence there is a clear need for alternative materials, which rival or exceed the performance of ITO and other more traditional electrode metals.<sup>[9,10]</sup>

Graphene, an isolated single layer of graphite, has received much attention in recent years as a promising transparent electrode material. The key challenges associated with its incorporation into practical electronic devices are finding scalable preparative routes and effective methods for laying down uniform films of graphene, ideally by existing proven deposition techniques. One promising method for preparing graphene is by chemical exfoliation of graphite oxide into graphene oxide sheets that can then be (partially) reduced to graphene by chemical and/or thermal treatments. Significant progress has been made recently in the wafer-scale deposition of chemically

Dr. P. H. Wöbkenberg, Dr. D.-S Leem, Prof. D. D. C. Bradley, Dr. T. D. Anthopoulos

Department of Physics and Centre for Plastic Electronics Blackett Laboratory

Imperial College London London SW7 2BW, UK

E-mail: thomas.anthopoulos@imperial.ac.uk

Dr. J. C. de Mello

Department of Chemistry and Centre for Plastic Electronics Imperial College London

London SW7 2AZ, UK

Dr. G. Eda, Prof. M. Chhowalla<sup>[+]</sup> Department of Materials Science Imperial College London London SW7 2AZ, UK

[+] Present address: Department of Materials Science and Engineering, Rutgers University, Piscataway, NJ 08854, USA

DOI: 10.1002/adma.201004161

derived graphene (CDG) resulting in proof-of-concept demonstrations of its use as electrodes in various electronic devices such as photovoltaic, [18–20] light-emitting diodes, [21,22] and organic transistors [23] employing a variety of deposition techniques. [12,24,25] To address the specific challenge of integrating CDG-based electrodes into wafer-scale circuits, however, compatible patterning techniques must also be developed.

Here we demonstrate the patterning of CDG electrodes for use in organic field-effect transistors using the interlayer lithography method. This technique has previously been presented by Huang et al.[2,27,28] and Leem et al.[3,29] for the micrometer-scale patterning of molecular electrode materials and carbon nanotubes. The interlayer technique involves the insertion of a layer of photoresist between the substrate and the film to be patterned. The resist layer is exposed through a mask, generating a pattern that can subsequently be developed after deposition of the target material. Immersion in an appropriate developer removes the soluble parts of the resist layer together with the overlying target material, leaving a patterned film of the target material over a likewise patterned film of the resist. The resist and the target material are in effect patterned simultaneously in an exposedeposit-develop step sequence. Furthermore, this technique is compatible with the use of standard solution processing and mechanical transfer methods for deposition of the target films. Since interlayer lithography builds on the existing expertise and equipment of conventional photolithography, it is easy to implement and fully compatible with fast, cost effective sheet-to-sheet processing for large-area electronics.

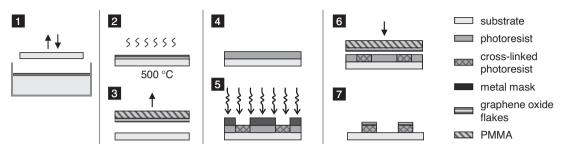

The electrode fabrication process is schematically depicted in Figure 1. A detailed description of the CDG layer preparation is reported in the Experimental Section and elsewhere. [25] Briefly, a suspension of partially oxidized graphene in N,N-dimethylformamide (DMF) was synthesized by mild oxidation and intercalation of graphite. After purification by repeated centrifugation, a monolayer of partially oxidized graphene was formed by Langmuir-Blodgett assembly on a water surface. Several monolayers of the CDG were transferred (by repeated dipping) onto a glass substrate (Figure 1, step 1) and then annealed at 500 °C for one hour (step 2) to induce thermal reduction. Langmuir-Blodgett assembly allows layer-by-layer deposition of CDG where each deposition yields one monolayer film with a thickness of approximately 1 nm. After reduction, the CDG film was then coated with a poly(methyl methacrylate) (PMMA) backing layer and released from the glass substrate (step 3) and the PMMA-backed-CDG was transferred (CDG face down) (step 6) onto a pre-exposed SU8-2 photoresist layer on a glass substrate (steps 4-6). (Note, although glass is used for the work reported here, the interlayer patterning method has previously been applied to a wide range

Figure 1. Interlayer lithography patterning of CDG electrodes. A thin film (4 nm) of CDG flakes is formed on a glass substrate by a Langmuir–Blodgett dip-coating technique (1). The CDG is partially reduced by annealing (2). Transfer of the conductive ultra-thin CDG layer by lamination onto exposed (4–5) SU8-2 photoresist with the help of a thin poly(methyl methacrylate) (PMMA) backing layer (3,6). Immersion in developer removes PMMA and un-crosslinked photoresist, resulting in patterned CDG electrodes with underlying crosslinked SU8-2 interlayer photoresist (7).

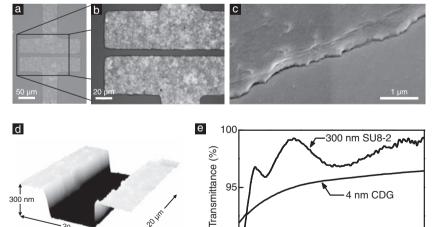

of other substrate materials including silicon, FR8 circuit board, and poly(ethylene terephthalate).) The entire substrate was then immersed in SU-8 developer and exposed to mild ultrasonication to yield the desired electrode pattern (step 7). A 4-layer CDG film, of approximately 4 nm thickness, exhibited transparency of ≈95% in the visible spectrum (Figure 2e) and had a sheet resistance of  $\approx 30 \text{ k}\Omega$  per square. In comparison, much thicker (tens of nm) ITO films with a transparency of ≈90% typically exhibit sheet resistance of in the order of 0.01–0.1 k $\Omega$  per square.<sup>[30]</sup> We note, however, that recent work by Kim et al. has shown that large-area graphene films prepared on thin nickel foils by chemical vapor deposition and subsequently transferred by an equivalent process onto quartz can exhibit low sheet resistances of 280  $\Omega$  per square with 80% optical transmission.<sup>[31]</sup> The patterned CDG source and drain electrodes shown in the optical microscopy images of Figures 2a,b are separated by a channel length of 10 µm. Here, a conventional metal shadow mask was used to expose the SU8-2 interlayer photoresist. With optimized photolithography masks, high resolution patterns down to the sub-micrometer regime can be routinely achieved<sup>[32]</sup> and have been previously demonstrated for interlayer lithography patterning of carbon nanotubess.<sup>[29]</sup> Figures 2c and d show the morphology of the CDG electrode edges and the underlying SU8-2 interlayer photoresist. No correlation between SU8-2 layer thickness and CDG electrode edge roughness could be observed. A possible explanation could be the ultra thin nature of the CDG electrodes as compared to the polymer layers.

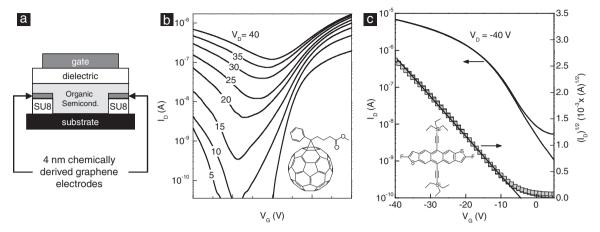

The combination of solid-state transfer and interlayer patterning is very versatile and was employed here for both top-gate (TG) and bottom-gate (BG) transistor architectures. TG transistors were fabricated by sequential spin coating of an organic semiconductor and a fluorinated polymer gate dielectric (CYTOP) onto the as-patterned CDG source—drain electrodes (Figure 3a). The patterning and deposition from solution of the latter two components is less demanding and could alternatively be achieved with a variety of printing or stamping techniques, since micrometer-scale resolution/registration is not required. Here we employed i) a solution processable methanofullerene ([6,6]-phenyl-C<sub>61</sub>-butyric

acid ester ([60]PCBM)) and ii) a binary blend comprising a small molecule (8-difluoro-5,11-bis(triethylsilylethynyl) anthradithiophene (diF-TESADT)) and a conjugated polymer (poly(triarylamine) (PTAA)) binder as two organic semiconductor exemplars.

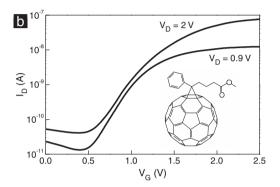

The devices with [60]PCBM demonstrate the extraordinary suitability of CDG as a universal electrode material that is capable of injecting both holes and electrons into the semiconductor layer as evident from the ambipolar transistor characteristics shown in Figure 3b. The work function of CDG is approximately 4.5 eV and the frontier orbitals of [60]PCBM are located at 6.1 and 3.7 eV. Hence, the barriers for charge injection from CDG into [60]PCBM are large at approximately 1.6 eV for holes and 0.8 eV for electrons. Despite these significant barriers, especially for hole injection, the transistor exhibits ambipolar transport characteristics and can be operated either in the hole or electron accumulation regime depending on the biasing conditions (Figure 3b). Hole and electron mobilities derived where in the order of  $10^{-3}$  and  $10^{-2}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively. This

Figure 2. Patterned CDG source and drain electrodes for thin-film transistors. a,b) Optical microscopy images of patterned CDG electrodes with a  $10\,\mu m$  channel length. c) Scanning electron microscopy image of the patterned electrode edge, taken at an angle of  $\approx 30^{\circ}$ . d) Atomic force microscopy image illustrating the profile of the elevated source and drain electrodes. e) Transmittance graph of a 4 nm CDG film and a 300 nm SU8-2 film on quartz.

90

600

Wavelength (nm)

800

www.MaterialsViews.com

**Figure 3.** Organic field-effect transistors employing CDG source–drain electrodes. a) Schematic representation of TG transistor architecture. Transfer (drain current vs gate voltage) characteristics of b) ambipolar [60]PCBM (channel dimensions  $L = 10 \, \mu m$ ,  $W = 200 \, \mu m$ ) and c) p-type diF-TESADT:PTAA ( $L = 40 \, \mu m$ ,  $W = 1000 \, \mu m$ ) transistors. The molecular structures of the semiconductors are shown as insets.

quality of CDG makes complex fabrication steps, often required for the patterning of different electrode materials, i.e., a high and a low work function one, in organic complementary logic, redundant. It also enables facile fabrication of complementary-like logic using ambipolar semiconductors such as [60]PCBM. CDG thus proves to be a very versatile electrode material that is airstable and can be processed in ambient conditions without any special precautions.

DiF-TESADT has been shown to be amongst the most promising solution-processable p-type organic semiconductors currently available. [24,33,34] Without further optimization of the blend composition and the electrode–semiconductor interface, hole mobilities of the order of 0.3 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> were achieved in TG transistors (Figure 3c). This performance is remarkable, given the simple solution processing and film transfer/patterning methods employed to prepare the CDG electrodes.

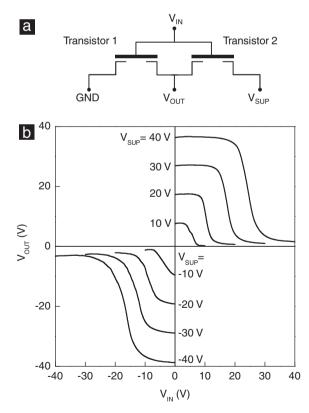

Moving towards the integration of individual devices into circuit architectures, we also demonstrate a complementary inverter (Figure 4), utilizing an ambipolar and a p-channel transistor. The circuit employs CDG as a single, universal injecting electrode material, deposited as before in the solution phase and patterned by interlayer lithography. The operational characteristics of the complementary inverter in the first and third quadrant with a gain of ≈8 are displayed in Figure 4b. In principle, larger, more complex circuits employing CDG as the material of choice for electrodes and interconnects could be patterned using the interlayer lithography method. Compared to conventional microelectronics based on gold as the conducting material, the approach presented here provides optical transparency, enables facile solution processing, and paves the way towards high-performance, large-area microelectronics.

Finally, we demonstrate the compatibility of interlayer patterned graphene electrodes with novel, transistor architectures. One major handicap of state-of-the-art organic electronic devices has been the large operating voltages (>20 V) and high power consumption, which prevent their utilization in portable electronic devices. This problem can be alleviated by introducing ultra-thin (≈2.1 nm) high capacitance gate dielectrics, such as

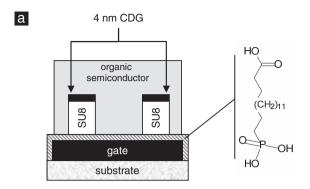

self-assembled monolayer dielectrics.<sup>[4,5]</sup> Here a phosphonohexadecanoic acid (**Figure 5a**) based self-assembled monolayer was functionalized on oxidized aluminium BG electrodes, followed by the interlayer lithographic patterning of the CDG source–drain electrodes. Remarkably, the patterning process is

**Figure 4.** Complementary inverter circuit with conducting CDG electrodes. a) Circuit diagram of the complementary inverter employing an ambipolar [60]PCBM transistor ( $L=30~\mu m,~W=500~\mu m$ ) and a p-channel diF-TESADT:PTAA transistor ( $L=40~\mu m,~W=1000~\mu m$ ). b) Output characteristics of an inverter operating in the first and the third quadrant with a maximum gain of  $\approx 8$ .

ADVANCED MATERIALS

www.advmat.de

www.advmat.c

**Figure 5.** Low operating voltage BG transistors. a) Schematic of the BG architecture employing a self-assembled monolayer gate dielectric. b) Transfer characteristics of a low-voltage [60]PCBM transistor employing patterned CDG source—drain electrodes. Chemical structures of [60]PCBM and the self-assembled monolayer dielectric are also shown.

sufficiently gentle as to preserve the monolayer gate dielectric beneath and allow fabrication of the novel transistor architecture shown in Figure 5a. Using this structure in combination with [60]PCBM as the organic semiconductor, an n-channel transistor with electron mobility of  $\approx\!10^{-2}~\rm cm^2~V^{-1}~s^{-1}$  and operation at voltages below 2.5 V has been achieved (Figure 5b). We note that this is the first demonstration of low-voltage operation for an organic transistor with CDG electrodes, an important requirement for practical application. We also emphasize that the dielectric, semiconductor, and source–drain electrodes are deposited from solution and all processes involved are compatible with easily scalable, large area deposition  $^{[25]}$  and patterning methodologies.

Another interesting characteristic of our BG device architecture incorporating the SU8-2 photoresist interlayer beneath the source–drain electrodes is the reduced parasitic capacitance compared to conventional self-assembled monolayer-based BG devices. [4,5] The capacitances of the photoresist interlayer and the monolayer gate dielectric amount to  $\approx$ 12 and  $\approx$ 600 nF cm<sup>-2</sup>, respectively, giving rise to a total parasitic capacitance between the source/drain electrodes and the gate of  $C_{\rm TOT} \approx 11.8$  nF cm<sup>-2</sup>. In a typical analogue bottom contact device the parasitic capacitance would equal that of the gate dielectric, i.e.,  $C_{\rm TOT} \approx 600$  nF cm<sup>-2</sup>. This drastically reduced parasitic capacitance is expected to yield transistors with faster operating speeds, as compared to conventional self-assembled monolayer based organic field-effect transistors with similar overlaps, [5] and presents an

additional incentive for interlayer lithographic patterning.<sup>[35]</sup> However, further work would be required in order to establish the significance of this alternative transistor architecture.

In summary, we have demonstrated a methodology that exploits the outstanding qualities of chemically derived graphene for use as a transparent electrode material in large-area organic electronic applications. With the help of a simplified and versatile photolithographic technique known as interlayer lithography, highly conductive ultra-thin solution processed CDG films were patterned into source and drain electrodes with gaps down to 10  $\mu m$ . Besides providing a suitable alternative to gold and transparent ITO electrodes, these patterned CDG electrodes allow for the fabrication of high performance field-effect transistors and complementary circuits that offer a viable route towards transparent organic electronics, fabricated entirely by solution processing.

## **Experimental Section**

Deposition and Transfer of Chemically Derived Graphene: Partially oxidized graphene was synthesized by exfoliation of mildly oxidized graphite. Graphite (Sigma-Aldrich) was treated in a mixture of nitric acid and potassium chlorate for one week and washed with a copious amount of water. The product was intercalated by tetrabutylammonium hydroxide (TBA) in DMF and exfoliated into individual sheets. The resulting suspension was centrifuged repeatedly to remove unexfoliated particles and TBA. The purified suspension was spread on a water surface dropwise until a continuous monolayer of partially oxidized graphene sheets was formed. The monolayer was deposited onto a glass substrate by contact transfer (dip-coating). The deposition was repeated four times to form a 4-layer film. Reduction of partially oxidized graphene was achieved by annealing at 500 °C in a forming gas for 1 h. The reduced film was coated with a PMMA backing layer, separated from its original substrate, and then transferred (CDG face down) with the backing layer still attached onto a pre-exposed SU 8 photoresist layer on a glass substrate.[25]

Interlayer Lithography: SU8-2 photoresist (Microchem) was diluted with SU 8 thinner in a 1:3 weight ratio and spin-coated onto clean glass at 4000 rpm for 40 s. The resist was soft-baked on a hot plate at 65 °C for 1 min and at 95 °C for 1 min, before being exposed to 250 mJ cm<sup>-2</sup> of 365 nm radiation using a Karl Suss MJB 3 mask aligner. After exposure, the resist was baked on a hot plate at 65 °C for 1 min and at 95 °C for 2 min. The CDG film (backed with PMMA) was laminated on top of the UV-exposed resist layer followed by annealing at 100 °C for 3 min. The CDG-coated resist layers were then developed using propylene glycol monomethyl ether acetate with the aid of mild sonication for 1 min, leaving a patterned layer of CDG on top of an identically patterned resist layer.

Transistor Fabrication and Characterization: For TG transistor architectures chlorobenzene solutions of [6,6]-phenyl-C<sub>61</sub>-butyric acid ester ([60]PCBM) (20 mg mL<sup>-1</sup>) or tetralin solutions of a 50:50 wt% 8-difluoro-5,11-bis(triethylsilylethynyl)anthradithiophene (diF-TESADT) with poly(triarylamine) (PTAA) were spin coated onto the interlayer lithography patterned CDG source-drain electrodes in a nitrogen atmosphere. As gate dielectric the fluoropolymer CYTOP (Asahi Glass Co.) was spin coated at 2000 rpm and dried at 90 °C for 15 min. An aluminium TG electrode was evaporated through a shadow mask. For the low operating voltage BG transistors, aluminium gate electrodes were evaporated through a shadow mask on to glass and their surface was oxidized by brief exposure to a low power, oxygen plasma. Phosphonohexadecanoic acid in isopropyl alcohol was drop cast onto and rinsed off the substrate (repeated several times to ensure full coverage), followed by baking at 140 °C for several hours. Patterning of the source-drain electrodes by interlayer lithography was then performed

on these substrates, in alignment with the previously deposited gate electrodes. Finally, the semiconductor layer ([60]PCBM) was deposited by spin-coating in a nitrogen atmosphere. All measurements were performed at room temperature in nitrogen atmosphere using a Keithley SCS4200 Semiconductor Parameter Analyzer.

## Acknowledgements

This work was funded by the UK Engineering and Physical Sciences Research Council (EPSRC-Grants EP/F023200 and EP/F061757), the Royal Society Brian Mercer Award for Innovation, and Research Councils UK (RCUK). M.C. and G.E. acknowledge the financial support from Center for Advanced Structural Ceramics (CASC) at Imperial College London. G.E. would like to acknowledge the Royal Society for the Newton International Fellowship. M.C. acknowledges support from the Royal Society through a Wolfson Merit Award.

> Received: November 10, 2010 Revised: January 1, 2011 Published online: March 1, 2011

- [1] S. Forrest, Nature 2004, 428, 911.

- [2] J. Huang, R. Xia, Y. Kim, X. Wang, J. Dane, O. Hofmann, A. Mosley, A. J. deMello, J. C. deMello, D. D. C. Bradley, J. Mater. Chem. 2007, *17*, 1043.

- [3] D.-S. Leem, P. H. Wöbkenberg, J. Huang, T. D. Anthopoulos, D. D. C. Bradley, J. C. deMello, Org. Electron. 2010, 11, 1307.

- [4] M. Halik, H. Klauk, U. Zschieschang, G. Schmid, C. Dehm, M. Schutz, S. Maisch, F. Effenberger, M. Brunnbauer, F. Stellacci, Nature 2004, 431, 963.

- [5] P. H. Wöbkenberg, J. Ball, F. B. Kooistra, J. C. Hummelen, D. M. de Leeuw, D. D. C. Bradley, T. D. Anthopoulos, Appl. Phys. Lett. 2008, 93, 013303.

- [6] J. Park, S. C. Lee, P. K. Song, Met. Mater. Int. 2007, 13, 475.

- [7] H. Kim, C. M. Gilmore, A. Pique, J. S. Horwitz, H. Mattoussi, H. Murata, Z. H. Kafafi, D. B. Chrisey, J. Appl. Phys. 1999, 86, 6451.

- [8] NanoMarkets, Indium Tin Oxide and Alternative Transparent Conductor Markets 2009, Nano-096, 7.

- [9] A. Kumar, C. Zhou, ACS Nano 2010, 4, 11.

- [10] L. Hu, J. Li, J. Liu, G. Grüner, T. Marks, Nanotechnology 2010, 21,

- [11] S. De, J. N. Coleman, ACS Nano 2010, 4, 2713.

- [12] S. Bae, H. Kim, Y. Lee, X. Xu, J.-S. Park, Y. Zheng, J. Balakrishnan, T. Lei, H. Ri Kim, Y. I. Song, Y.-J. Kim, K. S. Kim, B. Ozyilmaz, J.-H. Ahn, B. H. Hong, S. Iijima, Nat. Nanotechnol. 2010, 5, 574.

- [13] Y. Wang, X. Chen, Y. Zhong, F. Zhu, K. P. Loh, Appl. Phys. Lett. 2009, 95, 063302.

- [14] K. P. Loh, Q. Bao, P. K. Ang, J. Yang, J. Mater. Chem. 2010, 20, 2277.

- [15] S. Unarunotai, Y. Murata, C. E. Chialvo, N. Mason, I. Petrov, R. G. Nuzzo, J. S. Moore, J. A. Rogers, Adv. Mater. 2010, 22, 1072.

- [16] G. Eda, M. Chhowalla, Adv. Mater. 2010, 22, 2392.

- [17] H. c. A. Becerril, J. Mao, Z. Liu, R. M. Stoltenberg, Z. Bao, Y. Chen, ACS Nano 2008, 2, 463.

- [18] X. Wang, L. Zhi, K. Mullen, Nano Lett. 2007, 8, 323.

- [19] G. Eda, Y.-Y. Lin, S. Miller, C.-W. Chen, W.-F. Su, M. Chhowalla, Appl. Phys. Lett. 2008, 92, 233305.

- [20] J. Wu, H. A. Becerril, Z. Bao, Z. Liu, Y. Chen, P. Peumans, Appl. Phys. Lett. 2008, 92, 263302.

- [21] J. Wu, M. Agrawal, H. c. A. Becerril, Z. Bao, Z. Liu, Y. Chen, P. Peumans, ACS Nano 2009, 4, 43.

- [22] P. Matyba, H. Yamaguchi, G. Eda, M. Chhowalla, L. Edman, N. D. Robinson, ACS Nano 2010, 4, 637.

- [23] S. Pang, H. N. Tsao, X. Feng, K. Müllen, Adv. Mater. 2009, 21, 3488.

- [24] S. Wang, P. K. Ang, Z. Wang, A. L. L. Tang, J. T. L. Thong, K. P. Loh, Nano Lett. 2009, 10, 92.

- [25] H. Yamaguchi, G. Eda, C. Mattevi, H. Kim, M. Chhowalla, ACS Nano **2010**. 4, 524.

- [26] R. A. Street, W. S. Wong, S. E. Ready, M. L. Chabinyc, A. C. Arias, S. Limb, A. Salleo, R. Lujan, Mater. Today 2006, 9, 32.

- [27] J. Huang, X. Wang, Y. Kim, A. J. deMello, D. D. C. Bradley, J. C. deMello, Phys. Chem. Chem. Phys. 2006, 8, 3904.

- [28] J. Huang, R. Xia, Y. Kim, X. Wang, J. Dane, O. Hofmann, A. Mosley, A. J. deMello, J. C. deMello, D. D. C. Bradley, J. Mater. Chem. 2007, 17, 1043.

- [29] D. S. Leem, S. Kim, J. W. Kim, J. I. Sohn, A. Edwards, J. Huang, X. Wang, J.-J. Kim, D. D. C. Bradley, J. C. deMello, Small 2010, 6,

- [30] Praezisions Glas & Optik, ITO coatings on High Quality Glass Substrates, http://www.pgo-online.com/intl/katalog/ito.html, accessed February 2010.

- [31] K. S. Kim, Y. Zhao, H. Jang, S. Y. Lee, J. M. Kim, K. S. Kim, J.-H. Ahn, P. Kim, J.-Y. Choi, B. H. Hong, Nature 2009, 457, 706.

- [32] G. L. T. Chiu, J. M. Shaw, IBM J. Res. Dev. 1997, 41, 3.

- [33] D. J. Gundlach, J. E. Royer, S. K. Park, S. Subramanian, O. D. Jurchescu, B. H. Hamadani, A. J. Moad, R. J. Kline, L. C. Teague, O. Kirillov, C. A. Richter, J. G. Kushmerick, L. J. Richter, S. R. Parkin, T. N. Jackson, J. E. Anthony, Nat. Mater. 2008, 7, 216.

- [34] J. Smith, R. Hamilton, M. Heeney, D. M. de Leeuw, E. Cantatore, J. E. Anthony, I. McCulloch, D. D. C. Bradley, T. D. Anthopoulos, Appl. Phys. Lett. 2008, 93, 253301.

- [35] V. Wagner, P. H. Wöbkenberg, A. Hoppe, J. Seekamp, Appl. Phys. Lett. 2006, 89, 243515.